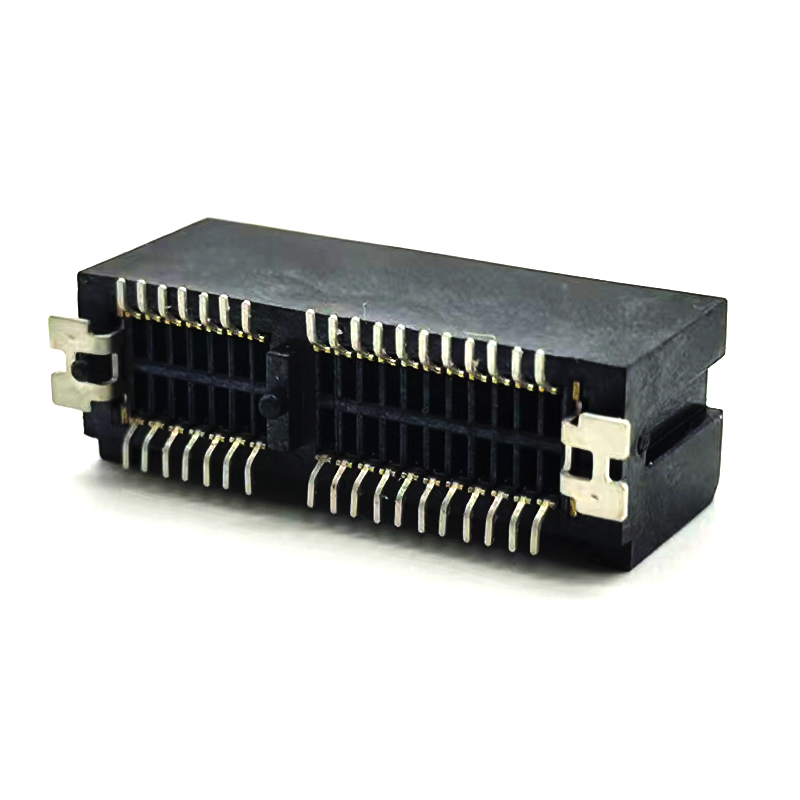

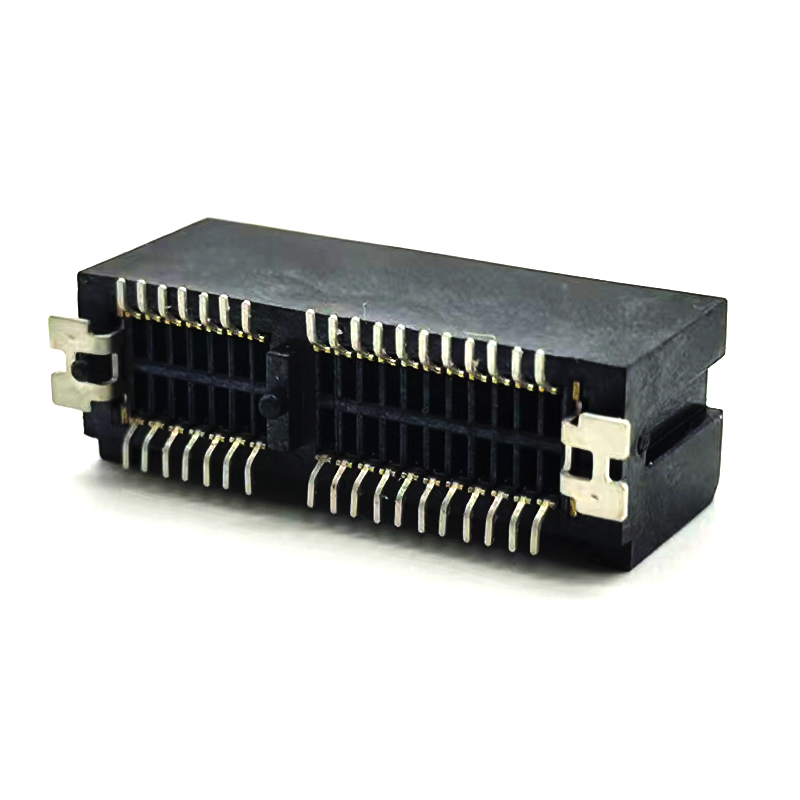

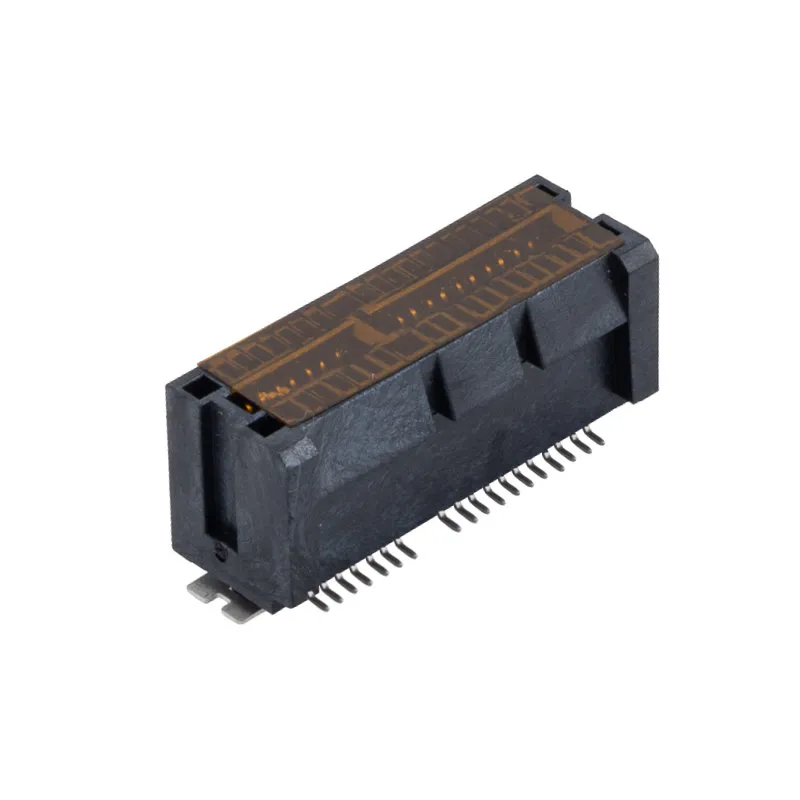

1.00mm Pitch PCI Express X1 card edge Connector 36 Circuits PCI-E vetical SMT Type

- Part No : PCIEVSM10-36GX

-

1. Current Rating : 1.1Amps

2. Voltage Rating : 250V AC

3. Contact Resistance : 30m Ohm Max At DC 100m Amps

4. Insulation Resistance : 100M Ohm Min At DC 500V

5. Withstanding Voltage : 1 Minute At 750V r.m.s Min

6. Operating Temperature Range : -40°C ~ 85°C

Meterials:

1.Insulator:High Temp. Plastic (Lcp UL94V-0) - Inquiry now

- Products Drawing

Detailed description

PCIe Gen4 products are engineered to deliver lightning-fast data transfer rates and unmatched performance, ushering in a new era of computing power and efficiency.

Melissa Lee

Email:sales05@dghoyato.com

Skype:limiao425

Phone/Whatsapp:86-13337908889

1.00mm Pitch PCI Express Connector 36 Circuits PCI-E vetical SMT Type

|

Connector Type

|

PCI-E vetical SMT Type,1.00mm Pitch PCI Express Connector,36 Circuits PCI-E,pcie riser card,Adapter Port Multiplier Card

|

|||

|

Orginal P/N

|

Replacement for molex,AMP

|

|||

|

Pitch – Mating

|

0.039″ (1.00mm)

|

|||

|

Number of Positions

|

36

|

|||

|

Number of rows

|

2

|

|||

|

Mounting Type

|

Vertical SMT Type

|

|||

|

Function

|

PCIE4.0 36P

|

|||

|

Plasting

|

Selective Gold Plated

|

|||

Why is PCIe Faster than PCI?

The evolution of computer interfaces has led to significant advancements in data transfer speeds and overall performance. One of the most notable developments in this realm is the transition from Peripheral Component Interconnect (PCI) to Peripheral Component Interconnect Express (PCIe). Understanding the reasons behind PCIe’s superior performance requires an examination of their architectures, signaling methods, and the role of the card edge connector.

#### Understanding PCI and PCIe

**Peripheral Component Interconnect (PCI)** was introduced in the early 1990s as a standard for connecting peripherals to the motherboard. It supports a 32-bit or 64-bit data bus and operates at a maximum clock speed of 33 MHz or 66 MHz, translating to a theoretical maximum bandwidth of 133 MB/s for 32-bit PCI and 266 MB/s for 64-bit PCI. While PCI served its purpose well during its time, it became evident that the increasing demand for higher data transfer rates necessitated a more efficient solution.

**Peripheral Component Interconnect Express (PCIe)**, introduced in the early 2000s, revolutionized this landscape. Unlike PCI, which operates on a shared bus architecture, PCIe employs a point-to-point architecture. This means that each device connected via PCIe has a dedicated link to the motherboard, allowing for simultaneous communication without the bottlenecks associated with shared buses.

#### Key Differences Between PCI and PCIe

1. **Architecture**:

— **PCI** uses a shared bus system where multiple devices communicate over the same data path. This leads to contention for bandwidth, especially when multiple devices are active simultaneously.

— **PCIe**, on the other hand, utilizes a switch-based point-to-point architecture that allows multiple devices to communicate with the CPU or other devices simultaneously without interference.

2. **Data Transfer Rates**:

— PCI operates with a maximum bandwidth of up to 266 MB/s in its 64-bit configuration.

— PCIe, in its first generation, offers a bandwidth of 2.5 GT/s (gigatransfers per second) per lane, which translates to approximately 250 MB/s per lane. PCIe is scalable, meaning that it can operate with multiple lanes. For instance, a PCIe x16 connection can provide a theoretical maximum bandwidth of 4 GB/s, which is a significant upgrade from PCI.

3. **Signal Encoding**:

— PCI uses parallel signaling, which can suffer from issues related to crosstalk and signal degradation over longer distances.

— PCIe employs differential signaling and 8b/10b encoding, which improves data integrity and reduces errors. The encoding scheme allows for efficient transmission of data and minimizes the overhead caused by error correction.

4. **Scalability**:

— PCI is limited in terms of scalability, as adding more devices can lead to a decrease in performance due to the shared bus architecture.

— PCIe’s design allows for greater scalability, with multiple lanes (x1, x4, x8, x16, etc.) that can be combined to increase bandwidth as needed. This flexibility makes PCIe suitable for a wide range of applications, from consumer electronics to enterprise-level systems.

5. **Latency**:

— PCI has higher latency due to the contention for shared resources.

— PCIe reduces latency significantly by allowing direct communication between devices and the CPU, enhancing overall system responsiveness.

#### The Role of the Card Edge Connector

A critical component in the physical connection of PCI and PCIe devices is the **card edge connector**. This connector is the interface through which a peripheral card interfaces with the motherboard. The design and implementation of the card edge connector have evolved alongside the transition from PCI to PCIe.

1. **Physical Design**:

— The PCI card edge connector is wider and accommodates a larger number of pins compared to the PCIe connector. This is due to the parallel nature of PCI signaling, which requires more physical connections to facilitate data transfer.

— In contrast, PCIe uses a narrower connector that supports fewer pins, reflecting its point-to-point architecture. The PCIe connector design allows for various lane configurations, enabling flexibility in bandwidth allocation.

2. **Signal Integrity**:

— PCIe’s card edge connector is designed to maintain signal integrity through its differential signaling approach. The layout of the pins and the design of the connector help minimize issues such as crosstalk and interference, which can hinder performance.

— PCI connectors do not have the same level of sophistication in terms of signal integrity, which can lead to performance bottlenecks, especially as speeds increase.

3. **Compatibility and Adaptability**:

— PCIe connectors are designed to be backward compatible with PCI, allowing older cards to be used in newer systems, albeit at PCI speeds. This adaptability has facilitated the transition to PCIe without rendering older hardware obsolete.

Conclusion

The transition from PCI to PCIe marks a significant advancement in computer architecture, driven by the need for faster, more efficient communication between peripherals and the motherboard. PCIe’s point-to-point architecture, higher data transfer rates, improved signal integrity, and scalability make it a superior choice for modern computing environments.

The role of the card edge connector cannot be understated in this evolution. Its design and functionality are critical for ensuring high-performance data transfer and compatibility across various systems. As technology continues to evolve, PCIe is likely to remain at the forefront of peripheral connectivity, paving the way for even faster and more efficient interfaces in the future.

In summary, PCIe’s architectural advantages, combined with the advancements in its card edge connector design, have established it as the preferred interface for high-speed data transfer in contemporary computing systems.